# FEATURES:

- 8 Mbit LPC Firmware Memory SuperFlash device with integrated LPC Keyboard, System configuration, and Power Management controller

- ACPI 2.0 Compliant

- Conforms to LPC Interface Specification v1.1

- Includes support for Multi-byte Firmware Memory Read/Write Cycles

- Firmware Memory 1-, 2-, 4-, 16-, and 128-byte Read Cycles

- Firmware Memory 1-, 2-, and 4-byte Write Cycles

- 15.7 MB/sec data transfer rate @ 33MHz clock for Multi-Byte Read

- One ID pin for LPC Firmware Memory Device selection

## • LPC Firmware Memory

- 8 Mbit Single Block of on-chip SuperFlash memory with two Shared-ROM modes

- Mode 1: 7 Mbit (896 KByte) for system BIOS and 1 Mbit (128 KByte) for 8051 firmware

- Mode 2: 7.5 Mbit (960 KByte) for system BIOS and 0.5 Mbit (64 KByte) for 8051 firmware

- Uniform 4 KByte Sectors and 64 KByte Blocks with Erase capability

- 19 Lockable Blocks: one 16 KByte Boot Block, two 8 KByte Parameter Blocks, one 32 KByte Parameter Block, fifteen 64 KByte Main Blocks

- Block Locking Registers for individual block Read-Lock, Write-Lock, and Lock Down protection

- Lockable bottom 4 KByte sector for 8051 boot firmware

- Erase-Suspend allowing Read or Program of the other blocks

Two-Cycle Command Set

## Non-Volatile Registers (NVR)

- 64-bit SST Pre-Programmed Identifier

- 192-bit OTP User Unique Identifier with Write-Lock protection

- 3 KByte OTP User NVR area (UNVR)

- 4 KByte Erasable NVR area (ÈNVR) with Write-/ Read-Lock protection

## • Superior Reliability

- Endurance: 100,000 Cycles (typical)

- Greater than 100 years Data Retention

## • Fast Erase/Program Operations

- Sector-Erase Time: 55 ms (typical)

- Block-Erase Time: 55 ms (typical)

- Word-Program Time: 15 µs (typical)

## aLPC mode for Rapid Factory Programming

- Alternate LPC bus (aLPC) for in-system and factory programming

- Auto Address Increment (AAI)

- Multi-Byte Program

- Chip Rewrite Time: 12 seconds (typical)

- Embedded Enhanced 8051 MCU

- 3- or 6-clock (selectable) per-instruction cycle

- Up to 33 MHz 8051 operating frequency

- Up to 128 KByte Program Address Space

- 256 Byte standard 8051 RAM

- 2 KByte on-chip expanded Data RAM / Executable RAM (Scratch ROM)

- Extended up to 2 KByte Stack Space

- Four Levels of Interrupt Priorities and Twelve Interrupt Vectors

- Power-saving IDLE and Power-Down modes

- Multiple Maskable Hardware Wake-up Events (sources include: Hibernation timer, LPC, serial interfaces, all GPIOs, and others)

## LPC Host Interfaces

- One 8042-style legacy KBC interface channel

- Two ACPI EC interface channels

- 32 8-bit LPC Host-to-8051 Mailbox Registers

- Programmable Base addresses for all channels

- System Interrupts

- IRQ1 and IRQ12 via serialized IRQ Interface

- Two EC SCI event outputs

- SMI via Serialized IRQ2 or SMI event output

- Hardware GA20 and CPU Reset Outputs Control

- 16 x 8 (24 pins) Key Scan Matrix expandable to 16 x 14 (30 pins)

- Three Independent PS/2 Ports

- Hardware driven receive and transmit protocols

Integrated time-out control

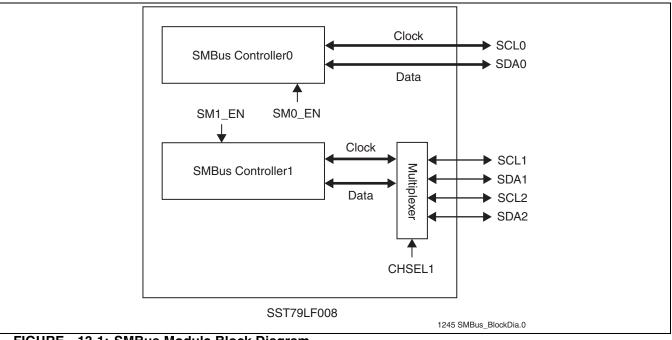

- Two SMBus controllers/Three SMBus channels

- SMBus 2.0 compliant

- Master and Slave operation

- Internal multiplexer for SMBus channel selection

- Full-Duplex Enhanced UART channel

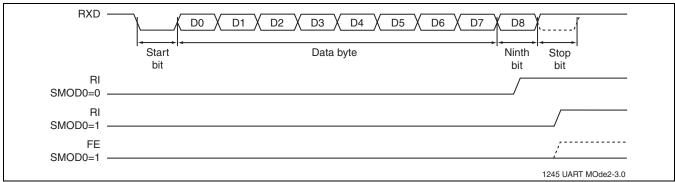

- SPI Master/Slave channel

- Eight-channel ADC with 10-bit resolution

- Four-channel DAC with 8-bit resolution

- Two 8-bit Fan Tachometer channels with clock

prescaler

- Three PWM channels with 8-bit resolution and independent prescaler

- Five direct LED control channels with blinking capability

- Watchdog Timer

- Hibernation Timer

- Three 16-bit Timers/Counters

- Configurable 5-Volt Tolerant General Purpose I/O Ports (GPIO)

- 112 GPIOs with 35 dedicated (non-multiplexed with alternative function)

- Any dedicated GPIO or GPIO with disabled alternative function can be configured as Edge-Trigger maskable Interrupt and/or Wake Up event

- Clocks

- Standard 32.768 KHz crystal oscillator

- 10 to 20MHz fail-safe internal ring oscillator (automatic switch-on if Power-Good signal is deasserted)

- Up to 33MHz core clock derived directly from the external clock input or via internal PLL

- Single 3.0-3.6V operation with 5V tolerant I/O (except LPC bus and analog I/O)

- Low Power Consumption

- Idle Mode supply current: 17mA (typical)

- Power-Down mode supply current: 100 µA (typical)

- Temperature Range: 0°C to 70°C

- Packages Available

- 176-lead LQFP

- 176-ball TFBGA

- All non-Pb (lead-free) devices are RoHS Compliant

# **PRODUCT DESCRIPTION**

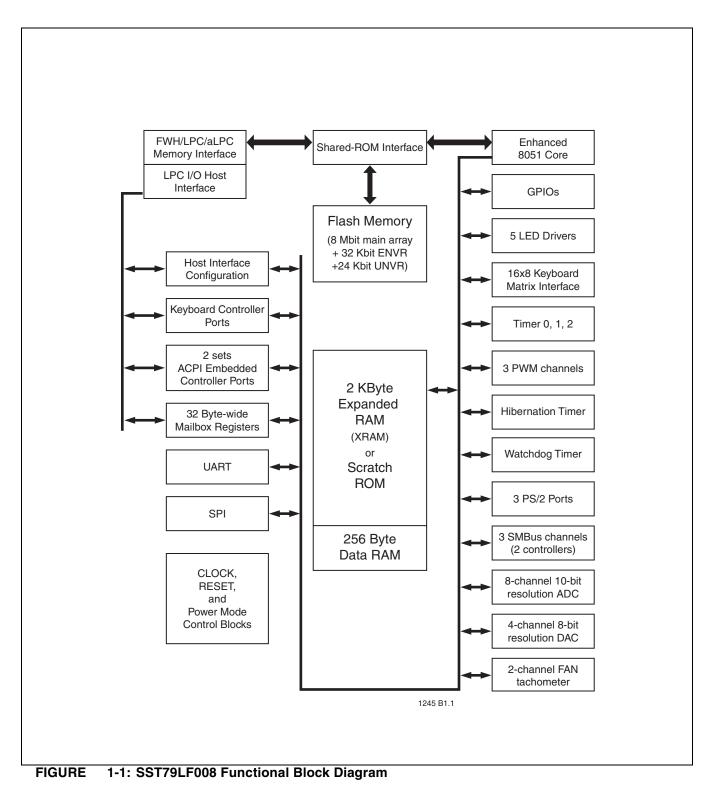

The SST79LF008 is a high-performance LPC flash device with integrated PC Keyboard/Auxiliary device controller (KBC) and ACPI embedded controller (EC). This product is well suited for a wide range of mobile internet computing applications which require high integration (small form factor), superior power, and thermal management capability.

SST79LF008 includes 8Mbit of SuperFlash memory, which can be used to store system BIOS as well as KBC/EC firmware. Either 128 KByte (1 Mbit) or 64 KByte (0.5 Mbit) of the SuperFlash memory can be allocated for the KBC/EC code providing, respectively, 896 KByte (7.0 Mbit) or 960 KByte (7.5 Mbit) for the system BIOS memory. The SST79LF008 features in-system programming, which provides maximum flexibility in the manufacturing environment as well as a mechanism for updating the keyboard firmware code, the main system BIOS code, and adding new functionality in the end-user environment in order to meet the latest market demands. It also speeds up software development and improves the overall time-to-market. The SST79LF008 is manufactured with SST's proprietary, high-performance SuperFlash technology. The split-gate cell design and thick-oxide tunneling injector attain better reliability and manufacturing capability compared with alternate approaches. The device significantly improves performance and reliability, while lowering the power consumption.

The SST79LF008 is designed to be compatible with any LPC bus compatible host controllers, such as the ICHx or other south-bridge devices of PC chipsets for PC-BIOS application. It provides several mechanisms controlled by KBC/EC firmware and/or LPC host for code and data storage protection. SST79LF008 also includes an additional 4 Kbyte of lockable, open-after-reset SuperFlash memory, which can be used as secure ENVR storage.

SST79LF008 on-chip peripherals, including PS/2 ports, Matrix scanner, SMBus controllers, and ADC/DAC/PWM with flexible GPIO configuration, provide necessary hardware support for the KBC/EC functions on the mobile PC platforms.

# **TABLE OF CONTENTS**

| 1.0 | FUNCTIONAL BLOCKS                                                                               | 15 |

|-----|-------------------------------------------------------------------------------------------------|----|

| 2.0 | PIN ASSIGNMENTS.                                                                                | 16 |

|     | 2.1 Pin Descriptions                                                                            | 18 |

|     | 2.2 I/O Type Descriptions.                                                                      |    |

| 20  | MEMORY ORGANIZATION                                                                             |    |

| 5.0 |                                                                                                 |    |

|     | 3.1 Program Memory                                                                              |    |

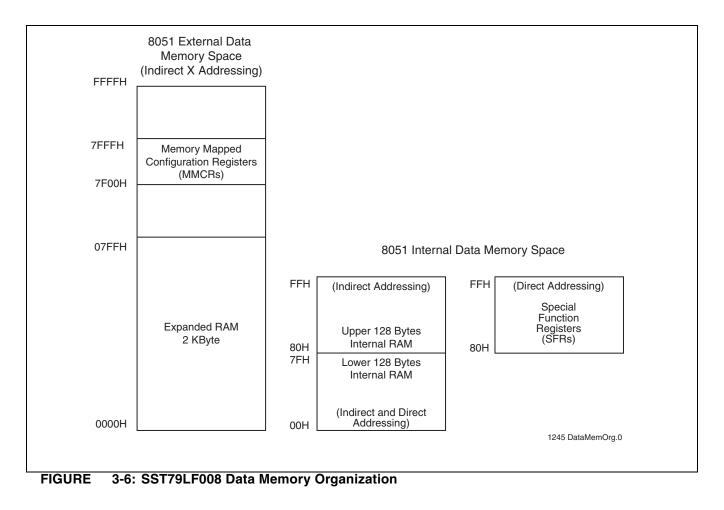

|     | 3.2 Data Memory                                                                                 |    |

|     | 3.3 Data Memory Addressing Modes.                                                               |    |

|     | 3.4 Special Function Registers (SFRs)                                                           |    |

|     | 3.4.1 SFR Map                                                                                   |    |

|     | 3.4.2 SFR References.                                                                           |    |

|     | 3.5 Memory Mapped Configuration Registers (MMCR)                                                |    |

|     | 3.5.1 MMCR References.                                                                          |    |

|     | 3.5.2 JEDEC Registers                                                                           | 42 |

| 4.0 | FLASH MEMORY PROGRAMMING                                                                        | 43 |

|     | 4.1 SuperFlash Memory Overview                                                                  | 43 |

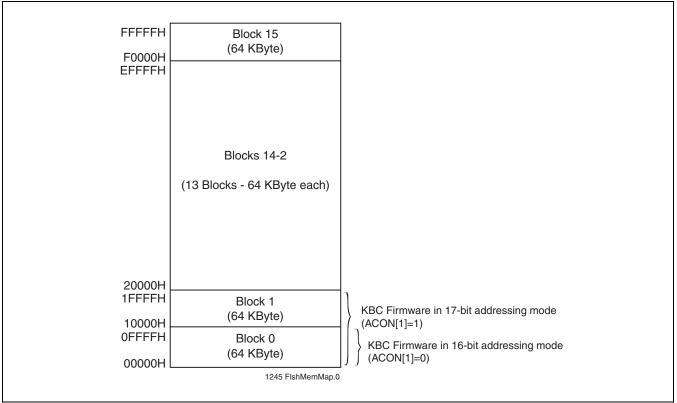

|     | 4.2 Flash Memory Map                                                                            | 44 |

|     | 4.2.1 ENVR / UNVR Address Space                                                                 | 44 |

|     | 4.2.2 Programming Modes                                                                         | 44 |

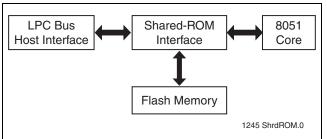

|     | 4.3 Shared ROM Interface                                                                        | 45 |

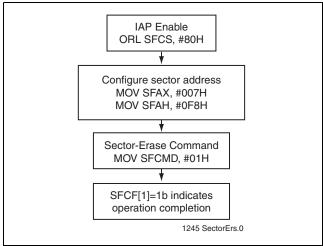

|     | 4.4 In-Application Programming Mode                                                             | 46 |

|     | 4.4.1 Scratch ROM Mapping Control                                                               | 46 |

|     | 4.4.2 IAP Mode Control                                                                          |    |

|     | 4.4.3 Address Selection for IAP Commands                                                        |    |

|     | 4.4.4 IAP Mode Commands Description                                                             |    |

|     | 4.4.4.1 No Operation                                                                            |    |

|     | 4.4.4.3 Block-Erase                                                                             |    |

|     | 4.4.4.4 Word-Program.                                                                           |    |

|     | 4.4.4.5 Erase-Suspend                                                                           |    |

|     | 4.4.4.6 Erase-Resume                                                                            | -  |

|     | 4.4.4.7 Word-Read                                                                               |    |

|     | 4.5 BootRom Area                                                                                |    |

|     | 4.6 LPC Flash Programming Mode                                                                  |    |

|     | 4.0 EFC Plash Programming Mode                                                                  |    |

|     | •                                                                                               |    |

|     | 4.8 aLPC MODE                                                                                   |    |

|     | 4.8.1       Alternate LPC (aLPC) Interface         4.8.2       aLPC Access to BIOS and KBC Code |    |

|     | 4.8.3 aLPC Memory Write Operation with Auto-Address Increment and Multi-Byte Programming        |    |

|     | 4.8.4 aLPC Memory Read Operation                                                                |    |

| Adva | Ince Information                                      |    |

|------|-------------------------------------------------------|----|

|      | 4.8.5 aLPC I/O Write Operation                        | 62 |

|      | 4.8.6 aLPC Flash Commands                             |    |

|      |                                                       |    |

| 5.0  | POWER, RESET AND CLOCK SOURCES                        | 66 |

|      | 5.1 Power Planes                                      | 66 |

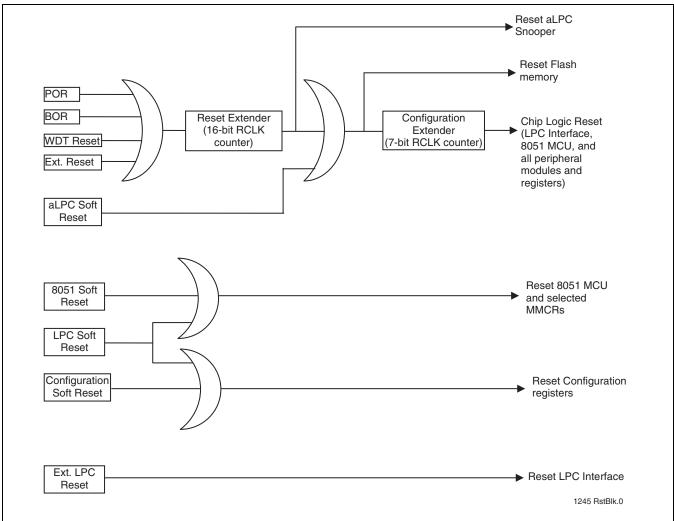

|      | 5.2 Reset Sources                                     | 66 |

|      | 5.2.1 Power-On Reset.                                 | 68 |

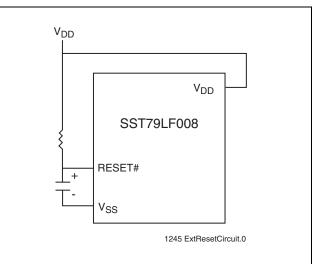

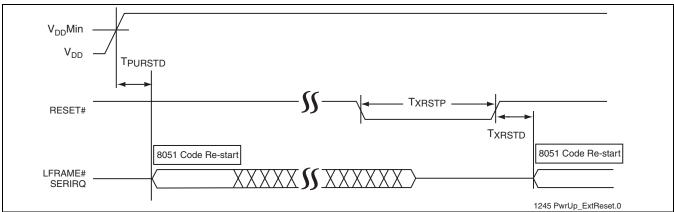

|      | 5.2.2 External Reset                                  | 69 |

|      | 5.2.3 Brown-out Detection Reset                       | 69 |

|      | 5.2.4 Watchdog Timer (WDT) Reset                      |    |

|      | 5.2.5 aLPC Soft Reset                                 |    |

|      | 5.2.6 LPC Soft Reset                                  |    |

|      | 5.2.7 8051 Firmware Soft Reset                        |    |

|      | 5.2.8 Configuration Soft Reset                        |    |

|      | 5.2.9 LPC Interface Reset.                            |    |

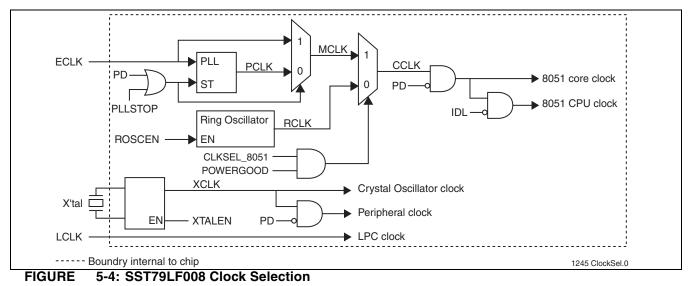

|      | 5.3 Clock Sources                                     |    |

|      | 5.3.1 Clock Input Options                             |    |

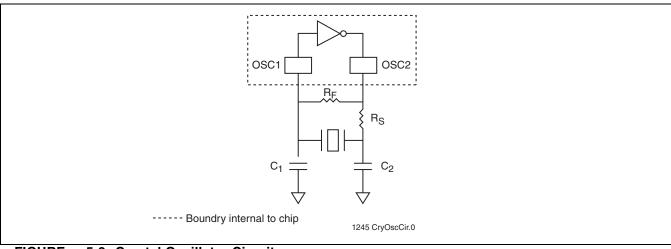

|      | 5.3.1.1 Crystal Oscillator                            |    |

|      | 5.3.2 Clock Selection Control and Clock Domains       |    |

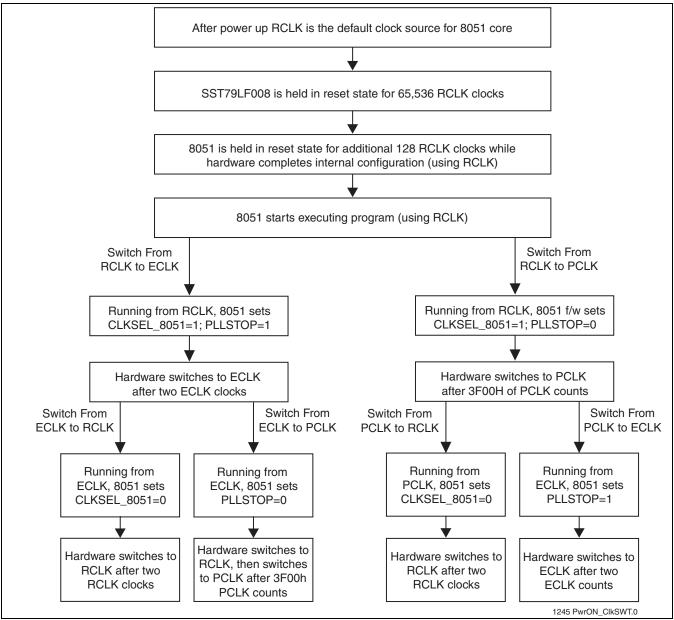

|      | 5.3.3 Clock Switching after Power On and Reset        |    |

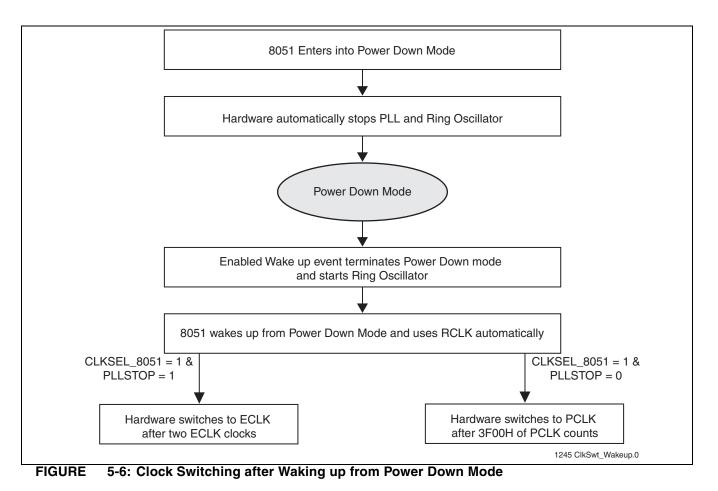

|      | 5.3.4 Clock Switching in Low Power Modes              |    |

|      |                                                       |    |

| 6.0  | 8051 EMBEDDED MICROCONTROLLER                         | 77 |

|      | 6.1 8051 MCU Enhancement.                             | 77 |

|      | 6.2 8051 Addressing Modes                             | 77 |

|      | 6.2.1 16-Bit Addressing Mode                          |    |

|      | 6.2.2 17-Bit Contiguous Addressing Mode               |    |

|      | 6.2.2.1 8051 Instruction Set Modifications            |    |

|      | 6.3 8051 Machine Cycle Control                        | 79 |

|      | 6.4 8051 Dual Data Pointers                           |    |

|      | 6.5 8051 Stack Extension                              |    |

|      |                                                       | 00 |

| 7.0  | LPC INTERFACE                                         | 82 |

|      | 7.1 LPC Bus Transfer.                                 | 82 |

|      | 7.2 LPC Bus Cycles                                    | 82 |

|      | 7.2.1 Firmware Memory Cycles.                         |    |

|      | 7.2.2 LPC Memory Cycles                               |    |

|      | 7.2.3 LPC I/O Cycles                                  |    |

|      | 7.3 LPC Flash Command Definitions                     | 89 |

|      | 7.3.1 Read Array Command                              |    |

|      | 7.3.2 Read Device Identifier Command                  |    |

|      | 7.3.3 Read Status Register Command                    |    |

|      | 7.3.4 Clear Status Register Command                   |    |

|      | 7.3.5 Sector Erase Command and Block Erase Command    |    |

|      | 7.3.6 Program Command                                 |    |

|      | 7.3.7 Erase Suspend Command and Erase Resume Commands | 91 |

|      | 7.3.8 User Unique ID Read, Program and Lockout Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 92                                                                                                                                                                                |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 7.3.10 Force / Release LPC Soft Reset Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                     |

|      | 7.4 LPC Abort Mechanism and Invalid Fields                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                     |

|      | 7.4.1 Response to Invalid Fields for Firmware Memory Cycle         7.4.2 Response to Invalid Fields for LPC Memory Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                     |

|      | 7.5 Multiple Device Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                     |

|      | 7.5.1 Multiple Device Selection for Firmware Memory Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                     |

|      | 7.5.2 Multiple Device Selection for LPC Memory Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                     |

|      | 7.6 LPC Memory Mapped Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                     |

|      | 7.6.1 Flash Memory Block Locking Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                     |

|      | 7.6.2 JEDEC ID Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                     |

|      | 7.6.3 Multi-byte Read/Write Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                     |

|      | 7.6.4 Unique ID Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                     |

|      | 7.7 PCI CLOCK RUN CONTROL SUPPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                     |

|      | 7.8 LPC Power Down Protocol Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 97                                                                                                                                                                                |

| 8.0  | INTERRUPTS AND WAKEUPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 98                                                                                                                                                                                |

|      | 8.1 SST79LF008 Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                     |

|      | 8.2 SST79LF008 Wakeups                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     |

|      | 8.3 INTERRUPT CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                     |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 101                                                                                                                                                                                 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 102                                                                                                                                                                                 |

| 9.0  | GPIO PORTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 123                                                                                                                                                                                 |

| 9.0  | 9.1 GPIO CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                     |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 123                                                                                                                                                                                 |

|      | 9.1 GPIO CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 123<br>141                                                                                                                                                                          |

|      | 9.1 GPIO CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 123<br>141<br>141                                                                                                                                                                   |

|      | 9.1 GPIO CONTROL REGISTERS         TIMERS/COUNTERS, WATCHDOG TIMER AND PWM         10.1 Timers: T0, T1, T2                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 123<br>141<br>141<br>141                                                                                                                                                            |

|      | 9.1 GPIO CONTROL REGISTERS<br>TIMERS/COUNTERS, WATCHDOG TIMER AND PWM<br>10.1 Timers: T0, T1, T2<br>10.2 Timer Operations<br>10.2.1 Timer 1 and Timer 0<br>10.2.1.1 Mode 0                                                                                                                                                                                                                                                                                                                                                                                                | 123<br>141<br>141<br>141<br>141<br>141                                                                                                                                              |

|      | 9.1 GPIO CONTROL REGISTERS<br>TIMERS/COUNTERS, WATCHDOG TIMER AND PWM<br>10.1 Timers: T0, T1, T2<br>10.2 Timer Operations<br>10.2.1 Timer 1 and Timer 0<br>10.2.1.1 Mode 0<br>10.2.1.2 Mode 1                                                                                                                                                                                                                                                                                                                                                                             | 123<br>141<br>141<br>141<br>141<br>141<br>141                                                                                                                                       |

|      | 9.1 GPIO CONTROL REGISTERS<br>TIMERS/COUNTERS, WATCHDOG TIMER AND PWM<br>10.1 Timers: T0, T1, T2<br>10.2 Timer Operations<br>10.2.1 Timer 1 and Timer 0<br>10.2.1.1 Mode 0                                                                                                                                                                                                                                                                                                                                                                                                | 123<br>141<br>141<br>141<br>141<br>141<br>141<br>141                                                                                                                                |

|      | 9.1 GPIO CONTROL REGISTERS<br>TIMERS/COUNTERS, WATCHDOG TIMER AND PWM<br>10.1 Timers: T0, T1, T2<br>10.2 Timer Operations<br>10.2.1 Timer 1 and Timer 0<br>10.2.1.1 Mode 0<br>10.2.1.2 Mode 1<br>10.2.1.3 Mode 2<br>10.2.1.4 Mode 3<br>10.2.2 Timer 2                                                                                                                                                                                                                                                                                                                     | 123<br>141<br>141<br>141<br>141<br>141<br>141<br>141<br>141<br>142                                                                                                                  |

|      | 9.1 GPIO CONTROL REGISTERS<br>TIMERS/COUNTERS, WATCHDOG TIMER AND PWM<br>10.1 Timers: T0, T1, T2<br>10.2 Timer Operations<br>10.2.1 Timer 1 and Timer 0<br>10.2.1.1 Mode 0<br>10.2.1.2 Mode 1<br>10.2.1.3 Mode 2<br>10.2.1.4 Mode 3<br>10.2.2 Timer 2<br>10.2.2.1 16-bit Timer/Counter Capture Mode                                                                                                                                                                                                                                                                       | <ol> <li>123</li> <li>141</li> <li>141</li> <li>141</li> <li>141</li> <li>141</li> <li>141</li> <li>141</li> <li>142</li> <li>142</li> </ol>                                        |

|      | 9.1 GPIO CONTROL REGISTERS         TIMERS/COUNTERS, WATCHDOG TIMER AND PWM         10.1 Timers: T0, T1, T2         10.2 Timer Operations         10.2.1 Timer 1 and Timer 0         10.2.1.1 Mode 0         10.2.1.2 Mode 1         10.2.1.3 Mode 2         10.2.1.4 Mode 3         10.2.2 Timer 2         10.2.2.1 16-bit Timer/Counter Capture Mode         10.2.2.2 16-bit Timer/Counter Auto-reload Mode                                                                                                                                                              | <ol> <li>123</li> <li>141</li> <li>141</li> <li>141</li> <li>141</li> <li>141</li> <li>141</li> <li>141</li> <li>142</li> <li>142</li> <li>142</li> <li>142</li> <li>142</li> </ol> |

|      | 9.1 GPIO CONTROL REGISTERS<br>TIMERS/COUNTERS, WATCHDOG TIMER AND PWM<br>10.1 Timers: T0, T1, T2<br>10.2 Timer Operations<br>10.2.1 Timer 1 and Timer 0<br>10.2.1.1 Mode 0<br>10.2.1.2 Mode 1<br>10.2.1.3 Mode 2<br>10.2.1.4 Mode 3<br>10.2.2 Timer 2<br>10.2.2.1 16-bit Timer/Counter Capture Mode<br>10.2.2.2 16-bit Timer/Counter Auto-reload Mode<br>10.2.2.3 Baud Rate Generator Mode                                                                                                                                                                                | 123<br>141<br>141<br>141<br>141<br>141<br>141<br>141<br>142<br>142<br>142                                                                                                           |

|      | 9.1 GPIO CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 123<br>141<br>141<br>141<br>141<br>141<br>141<br>142<br>142<br>142<br>142                                                                                                           |

|      | 9.1 GPIO CONTROL REGISTERS .<br>TIMERS/COUNTERS, WATCHDOG TIMER AND PWM .<br>10.1 Timers: T0, T1, T2 .<br>10.2 Timer Operations .<br>10.2.1 Timer 1 and Timer 0.<br>10.2.1.1 Mode 0 .<br>10.2.1.2 Mode 1 .<br>10.2.1.3 Mode 2 .<br>10.2.1.4 Mode 3 .<br>10.2.2 Timer 2.<br>10.2.2.1 16-bit Timer/Counter Capture Mode .<br>10.2.2.2 I6-bit Timer/Counter Auto-reload Mode .<br>10.2.2.3 Baud Rate Generator Mode .<br>10.3 Timers/Counter SFRs.<br>10.4 Watchdog Timer (WDT) .                                                                                            | 123<br>141<br>141<br>141<br>141<br>141<br>141<br>142<br>142<br>142<br>142                                                                                                           |

|      | 9.1 GPIO CONTROL REGISTERS<br>TIMERS/COUNTERS, WATCHDOG TIMER AND PWM<br>10.1 Timers: T0, T1, T2<br>10.2 Timer Operations.<br>10.2.1 Timer 1 and Timer 0.<br>10.2.1.1 Mode 0<br>10.2.1.2 Mode 1<br>10.2.1.2 Mode 1<br>10.2.1.3 Mode 2<br>10.2.1.4 Mode 3<br>10.2.2 Timer 2.<br>10.2.2.1 16-bit Timer/Counter Capture Mode<br>10.2.2.2 16-bit Timer/Counter Auto-reload Mode<br>10.2.2.3 Baud Rate Generator Mode<br>10.3 Timers/Counters SFRs.<br>10.4 Watchdog Timer (WDT).<br>10.4.1 Watchdog Timer MMCRs.                                                              | 123<br>141<br>141<br>141<br>141<br>141<br>141<br>142<br>142<br>142<br>142                                                                                                           |

|      | 9.1 GPIO CONTROL REGISTERS .<br>TIMERS/COUNTERS, WATCHDOG TIMER AND PWM .<br>10.1 Timers: T0, T1, T2 .<br>10.2 Timer Operations .<br>10.2.1 Timer 1 and Timer 0 .<br>10.2.1.1 Mode 0 .<br>10.2.1.2 Mode 1 .<br>10.2.1.3 Mode 2 .<br>10.2.1.4 Mode 3 .<br>10.2.2 Timer 2 .<br>10.2.2 1 16-bit Timer/Counter Capture Mode .<br>10.2.2 1 16-bit Timer/Counter Auto-reload Mode .<br>10.2.2.3 Baud Rate Generator Mode .<br>10.3 Timers/Counters SFRs.<br>10.4 Watchdog Timer (WDT) .<br>10.4.1 Watchdog Timer MMCRs.<br>10.5 Hibernation Timer .                             | 123<br>141<br>141<br>141<br>141<br>141<br>141<br>142<br>142<br>142<br>142                                                                                                           |

|      | 9.1 GPIO CONTROL REGISTERS<br>TIMERS/COUNTERS, WATCHDOG TIMER AND PWM<br>10.1 Timers: T0, T1, T2<br>10.2 Timer Operations.<br>10.2.1 Timer 1 and Timer 0.<br>10.2.1.1 Mode 0<br>10.2.1.2 Mode 1<br>10.2.1.2 Mode 1<br>10.2.1.3 Mode 2<br>10.2.1.4 Mode 3<br>10.2.2 Timer 2.<br>10.2.2.1 16-bit Timer/Counter Capture Mode<br>10.2.2.2 16-bit Timer/Counter Auto-reload Mode<br>10.2.2.3 Baud Rate Generator Mode<br>10.3 Timers/Counters SFRs.<br>10.4 Watchdog Timer (WDT).<br>10.4.1 Watchdog Timer MMCRs.                                                              | 123<br>141<br>141<br>141<br>141<br>141<br>141<br>142<br>142<br>142<br>142                                                                                                           |

| 10.0 | 9.1 GPIO CONTROL REGISTERS<br>TIMERS/COUNTERS, WATCHDOG TIMER AND PWM<br>10.1 Timers: T0, T1, T2<br>10.2 Timer Operations<br>10.2.1 Timer 1 and Timer 0<br>10.2.1.1 Mode 0<br>10.2.1.2 Mode 1<br>10.2.1.3 Mode 2<br>10.2.1.4 Mode 3<br>10.2.2 Timer 2<br>10.2.2.1 16-bit Timer/Counter Capture Mode<br>10.2.2.2 16-bit Timer/Counter Auto-reload Mode<br>10.2.2.3 Baud Rate Generator Mode<br>10.3 Timers/Counters SFRs.<br>10.4 Watchdog Timer (WDT)<br>10.4.1 Watchdog Timer MMCRs<br>10.5 Hibernation Timer.<br>10.6 Pulse Width Modulators (PWM)<br>10.6.1 PWM MMCRs. | 123<br>141<br>141<br>141<br>141<br>141<br>141<br>141<br>142<br>142<br>142                                                                                                           |

| 10.0 | 9.1 GPIO CONTROL REGISTERS .<br>TIMERS/COUNTERS, WATCHDOG TIMER AND PWM .<br>10.1 Timers: T0, T1, T2 .<br>10.2 Timer Operations .<br>10.2.1 Timer 1 and Timer 0.<br>10.2.1.1 Mode 0 .<br>10.2.1.2 Mode 1 .<br>10.2.1.2 Mode 1 .<br>10.2.1.3 Mode 2 .<br>10.2.2 Timer 2 .<br>10.2.2 Timer 2 .<br>10.2.2.2 16-bit Timer/Counter Capture Mode .<br>10.2.2.3 Baud Rate Generator Mode .<br>10.3 Timers/Counters SFRs.<br>10.4 Watchdog Timer (WDT) .<br>10.4.1 Watchdog Timer MMCRs .<br>10.5 Hibernation Timer.<br>10.6 Pulse Width Modulators (PWM) .                       | 123<br>141<br>141<br>141<br>141<br>141<br>141<br>142<br>142<br>142<br>142                                                                                                           |

| Advance Information                                               |       |  |

|-------------------------------------------------------------------|-------|--|

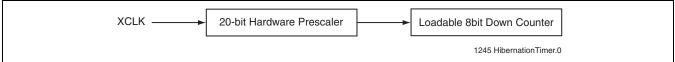

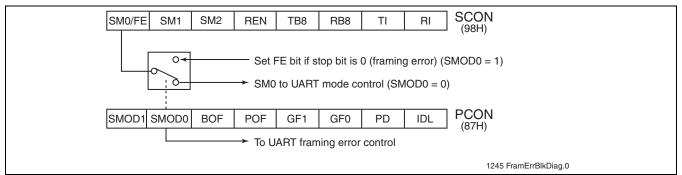

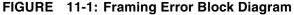

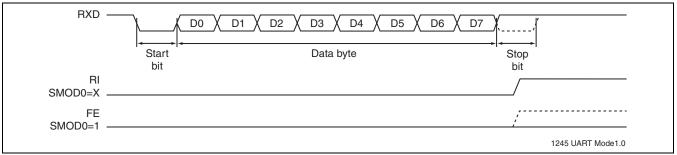

| 11.2 Framing Error Detection                                      | . 154 |  |

| 11.3 Automatic Address Recognition                                | . 155 |  |

| 11.3.1 Using the Given Address to Select Slaves                   | . 155 |  |

| 11.3.2 Using the Broadcast Address to Select Slaves               |       |  |

| 11.4 UART SFRs                                                    | . 157 |  |

| 12.0 SERIAL PERIPHERAL INTERFACE (SPI)                            | . 159 |  |

| 12.1 SPI Features                                                 | . 159 |  |

| 12.2 SPI Description                                              |       |  |

| 12.3 SPI Transfer Formats.                                        | . 160 |  |

| 12.4 SPI SFRs                                                     | . 161 |  |

| 13.0 SMBUS INTERFACE                                              | . 163 |  |

| 13.1 SMBus Features                                               |       |  |

| 13.2 SMBus Channels                                               |       |  |

| 13.3 SMBus Protocol Overview                                      |       |  |

| 13.4 SMBus MMCRs                                                  |       |  |

| 13.5 SMBus Multi-master Control and Status Registers              |       |  |

| 13.6 Multi-master Bus Address and Data Shift Registers            | . 169 |  |

| 13.7 SMBus Switch Control and Line Status Registers               | . 171 |  |

| 13.8 SMBus Operations                                             | . 171 |  |

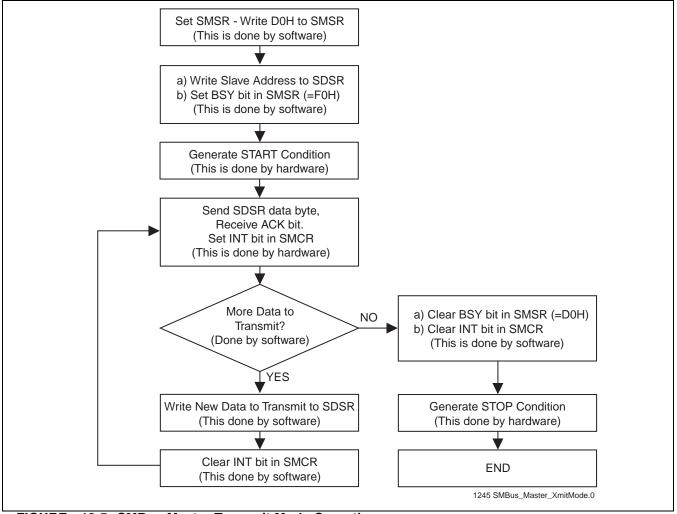

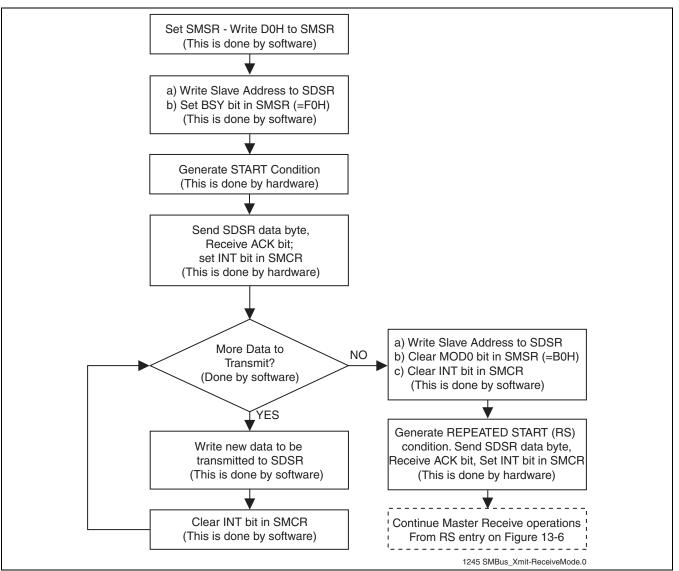

| 13.8.1 Master Transmit Mode                                       |       |  |

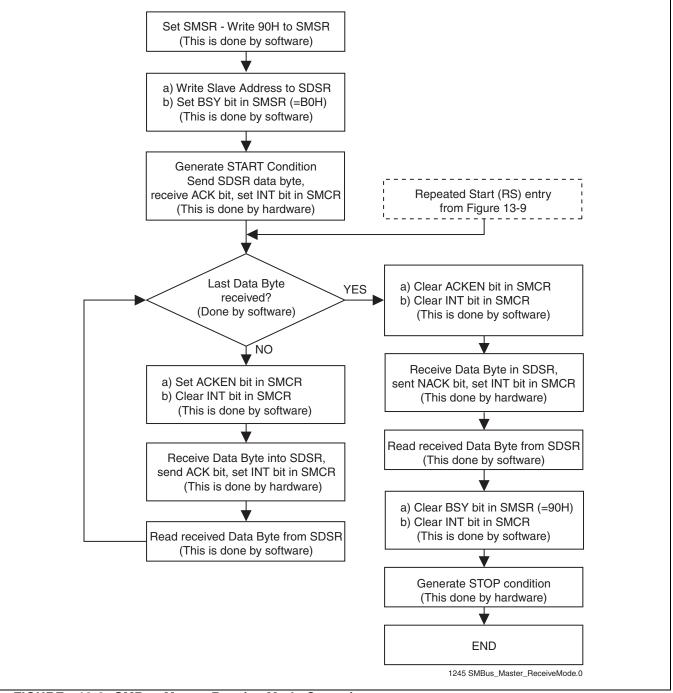

| 13.8.2 Master Receive Mode                                        |       |  |

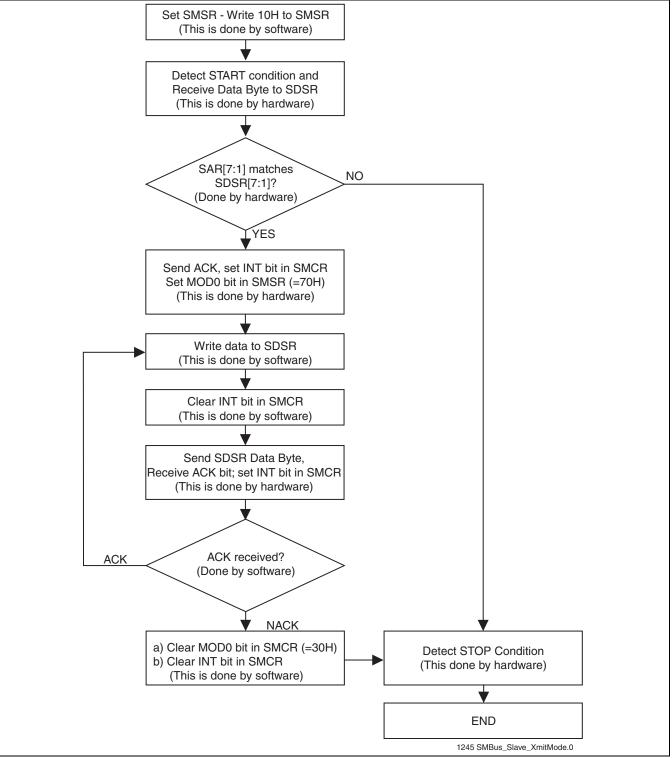

| 13.8.3 Slave Transmit Mode                                        |       |  |

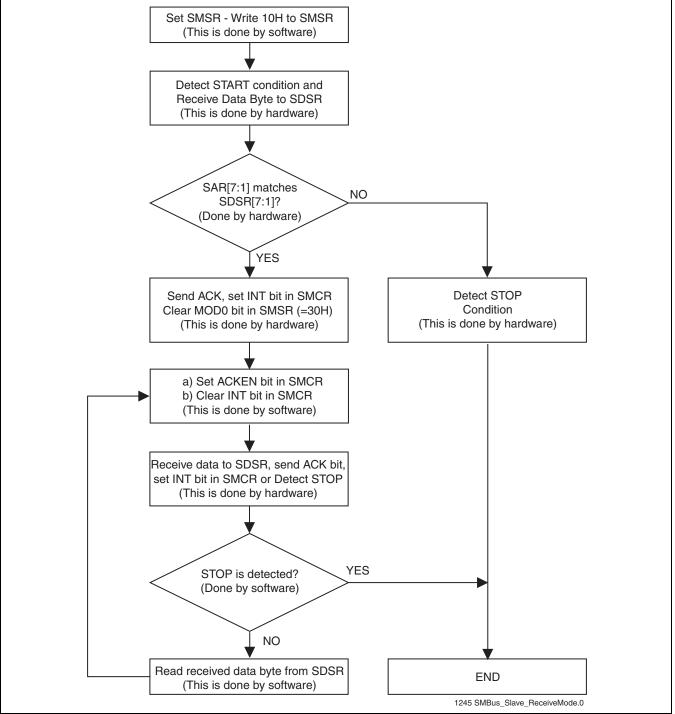

| 13.8.5 Switching Between Master Transmit and Master Receive Modes |       |  |

|                                                                   |       |  |

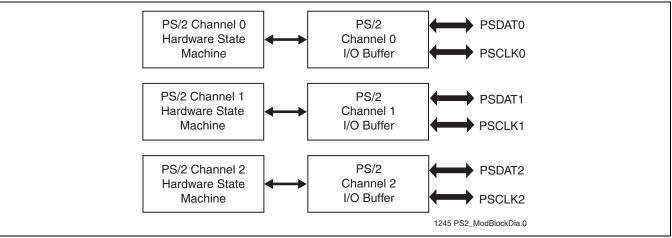

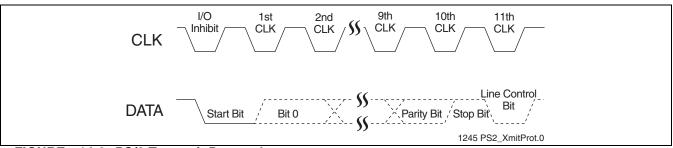

| 14.0 PS/2 INTERFACE                                               | . 181 |  |

| 14.1 PS/2 Features                                                | . 181 |  |

| 14.2 PS/2 Channels                                                | -     |  |

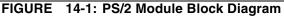

| 14.3 PS/2 Protocol Overview                                       |       |  |

| 14.4 PS/2 MMCRs                                                   |       |  |

| 14.4.1 PS/2 Transmit Registers                                    |       |  |

| 14.4.2 PS/2 Receive Registers                                     |       |  |

| 14.4.4 PS/2 Status Registers                                      |       |  |

| 14.4.5 PS/2 Time-out and Status 2 Registers                       |       |  |

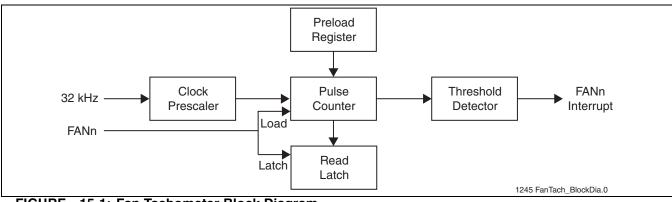

| 15.0 FAN TACHOMETERS                                              | . 191 |  |

| 15.1 Fan Tachometer Features                                      | . 191 |  |

| 15.2 Fan Tachometer Operation                                     |       |  |

| 15.3 Fan Tachometers MMCRs                                        |       |  |

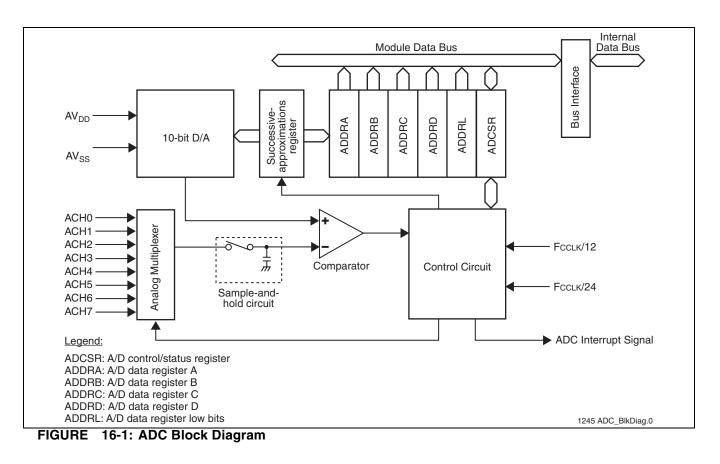

| 16.0 ANALOG TO DIGITAL CONVERTER (ADC)                            | . 194 |  |

| 16.1 ADC Features                                                 |       |  |

|      | 16.2 ADC MMCRs                                                                     | 195 |

|------|------------------------------------------------------------------------------------|-----|

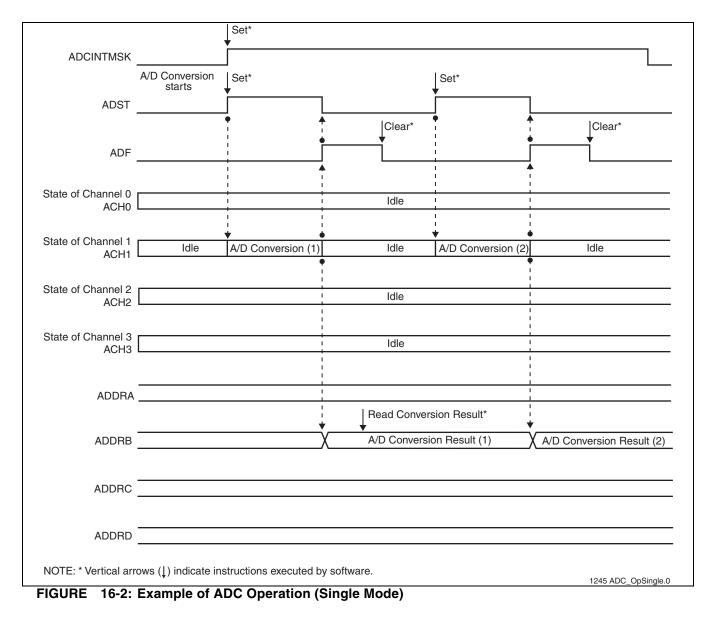

|      | 16.3 ADC Operations                                                                | 197 |

|      | 16.3.1 Single Mode                                                                 | 198 |

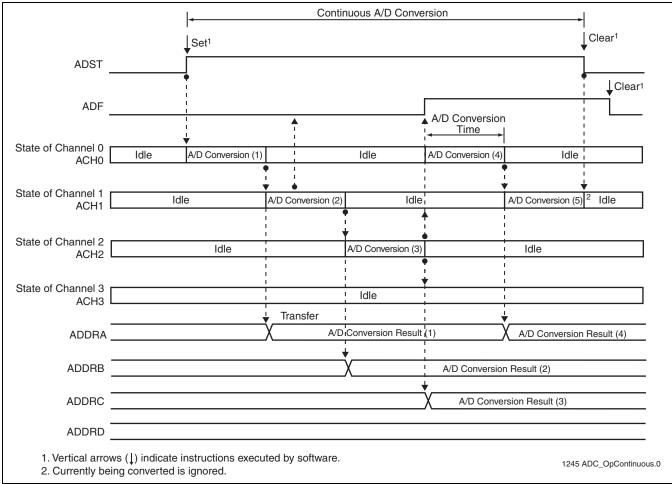

|      | 16.3.2 Continuous Mode                                                             | 199 |

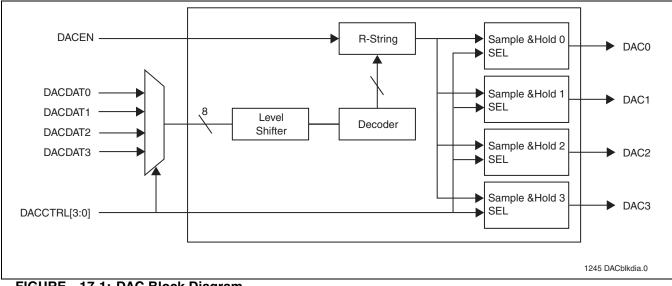

| 17.0 | DIGITAL TO ANALOG CONVERTOR (DAC)                                                  | 201 |

|      | 17.1 DAC Features                                                                  | 201 |

|      | 17.2 DAC MMCRs                                                                     | 202 |

|      | 17.3 DAC Operations                                                                |     |

|      | 17.3.1 Output Voltage                                                              |     |

|      | 17.3.2 Conversion Cycle                                                            |     |

|      | 17.3.3 DAC Channel Control                                                         |     |

|      |                                                                                    |     |

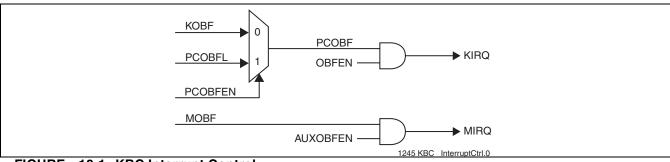

| 18.0 | KEYBOARD CONTROLLER HOST INTERFACE                                                 |     |

|      | 18.1 Keyboard Controller Interface Overview                                        |     |

|      | 18.2 Keyboard Controller Interface MMCRs         18.3 Keyboard Matrix Scan Control |     |

|      |                                                                                    |     |

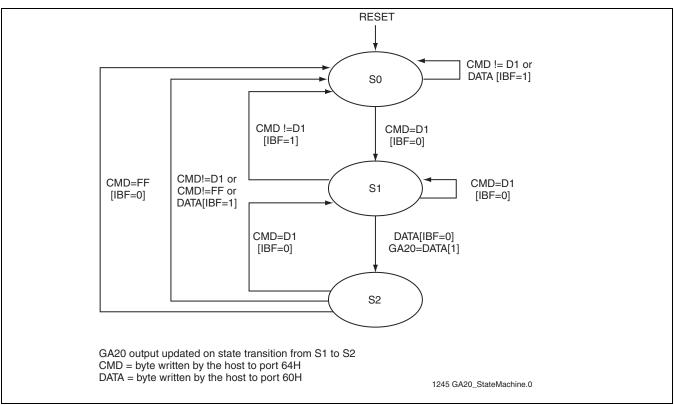

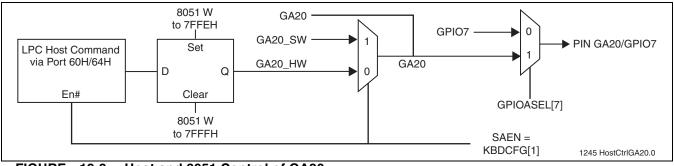

| 19.0 | GA20 AND CPU RESET HARDWARE CONTROL                                                |     |

|      | 19.1 GA20 State Machine                                                            |     |

|      | 19.2 GA20 and KBRST# MMCRs                                                         | 211 |

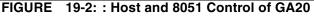

| 20.0 | ACPI EMBEDDED CONTROLLER INTERFACE                                                 | 213 |

|      | 20.1 ACPI Embedded Controller Interface Overview                                   |     |

|      | 20.2 Embedded Controller Interface MMCRs                                           |     |

|      | 20.3 SMI and SCI Control                                                           | 217 |

| 21.0 | MAILBOX INTERFACE AND DATA TRANSFER BLOCK                                          | 220 |

|      | 21.1 Mailbox Command/Data Transfer Registers                                       | 220 |

|      | 21.2 Mailbox Control Registers                                                     | 222 |

| 22.0 | SERIALIZED INTERRUPTS                                                              | 224 |

|      | 22.1 Serialized IRQ Cycle Overview                                                 | 224 |

|      | 22.2 Serialized IRQ Start Frame                                                    | 224 |

|      | 22.3 Serialized IRQ Data Frame                                                     | 225 |

|      | 22.4 Serialized IRQ Stop Frame                                                     | 225 |

| 23.0 | SST79LF008 CONFIGURATION                                                           | 226 |

|      | 23.1 Access to Configuration Registers                                             | 226 |

|      | 23.2 Configuration Registers Description.                                          | 228 |

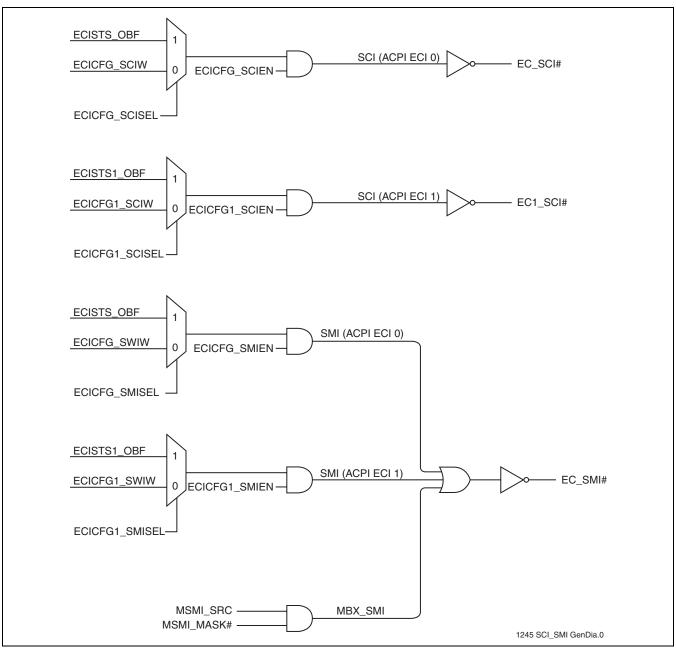

| 24.0 | ELECTRICAL SPECIFICATION                                                           | 230 |

|      | 24.1 Absolute Maximum Stress Ratings                                               | 230 |

|      | 24.2 Operating Conditions                                                          |     |

|      | 24.3 DC Electrical Characteristics               | 231 |

|------|--------------------------------------------------|-----|

|      | 24.4 AC Electrical Characteristics               | 234 |

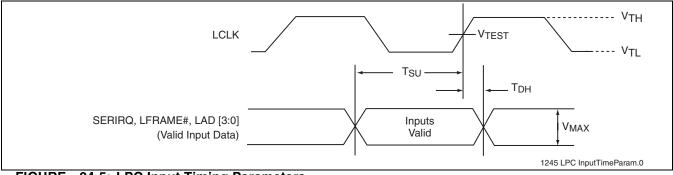

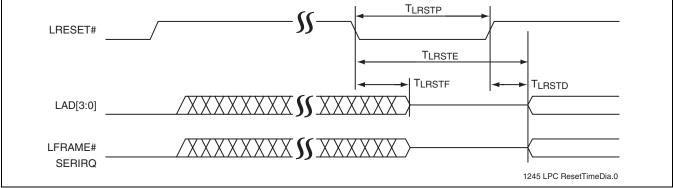

|      | 24.4.1 LPC Interface and Firmware Memory Timing. | 234 |

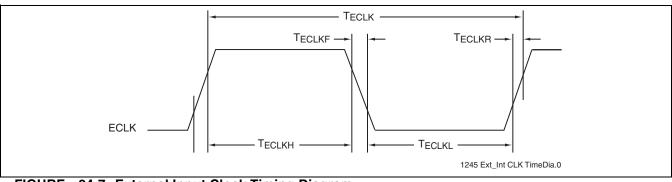

|      | 24.4.2 External Clocks and Reset Timing          | 238 |

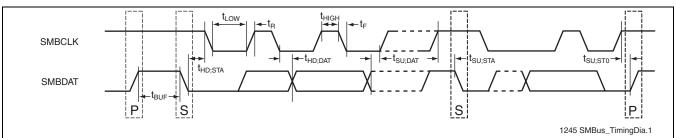

|      | 24.4.3 SMBus Interface Timing                    | 239 |

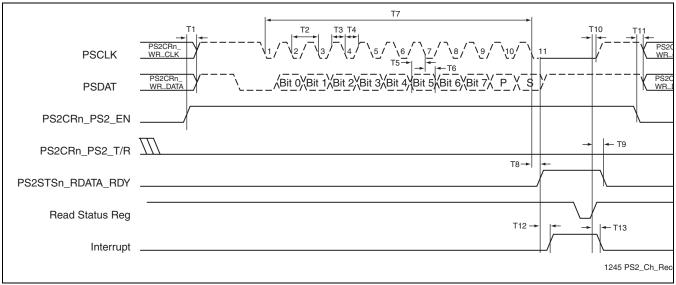

|      | 24.4.4 PS/2 Interface Timing                     | 240 |

|      | 24.4.5 UART Timing                               | 243 |

|      | 24.4.6 SPI Timing                                | 244 |

|      | 24.4.7 PWM and FAN Tachometer Timing             | 247 |

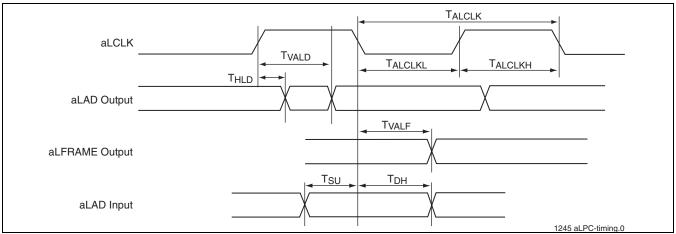

|      | 24.4.8 aLPC Interface Timing                     | 248 |

|      | 24.5 Analog Characteristics                      | 249 |

|      | 24.5.1 ADC Characteristics                       | 249 |

|      | 24.5.2 DAC Characteristics                       | 249 |

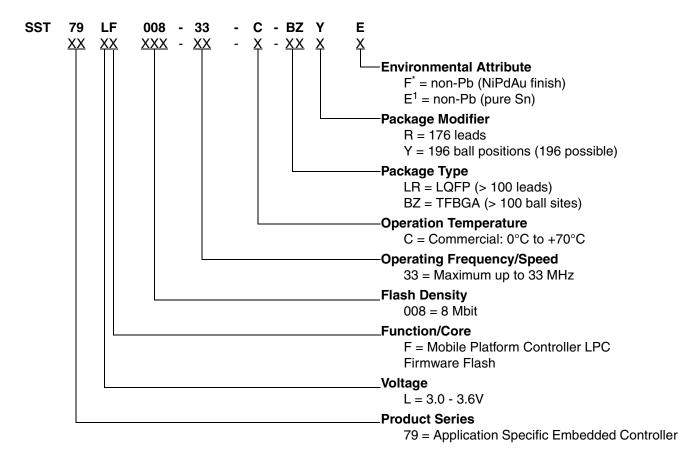

| 25.0 | PRODUCT ORDERING INFORMATION                     | 250 |

|      | 25.1 Valid Combinations                          | 250 |

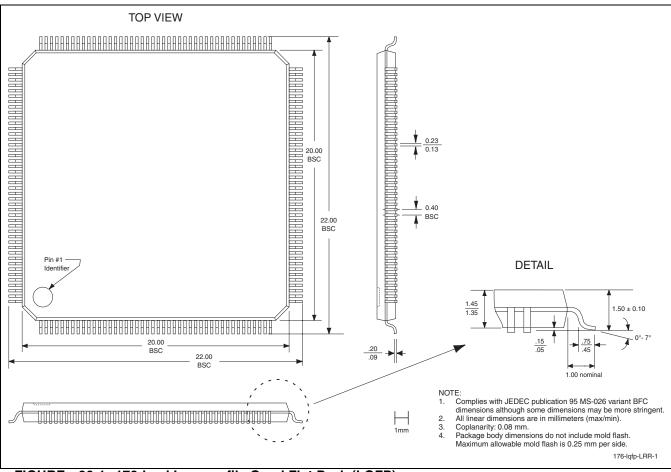

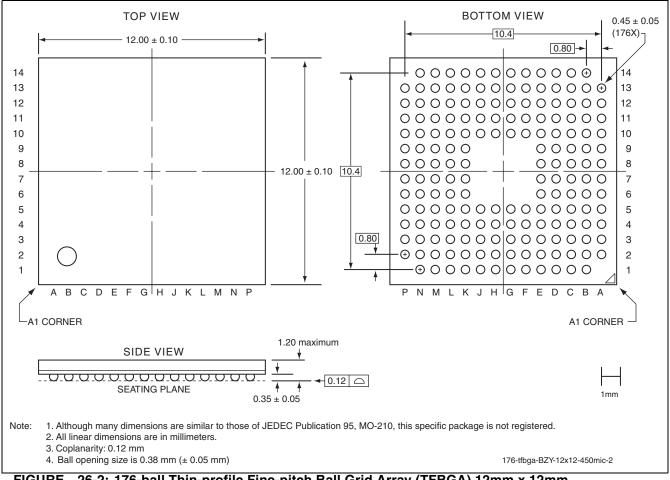

| 26.0 | PACKAGING DIAGRAMS                               | 251 |

# **LIST OF FIGURES**

| FIGURE 1-1: SST79LF008 Functional Block Diagram                                   |

|-----------------------------------------------------------------------------------|

| FIGURE 2-1: Pin Assignments for 176-ball TFBGA 16                                 |

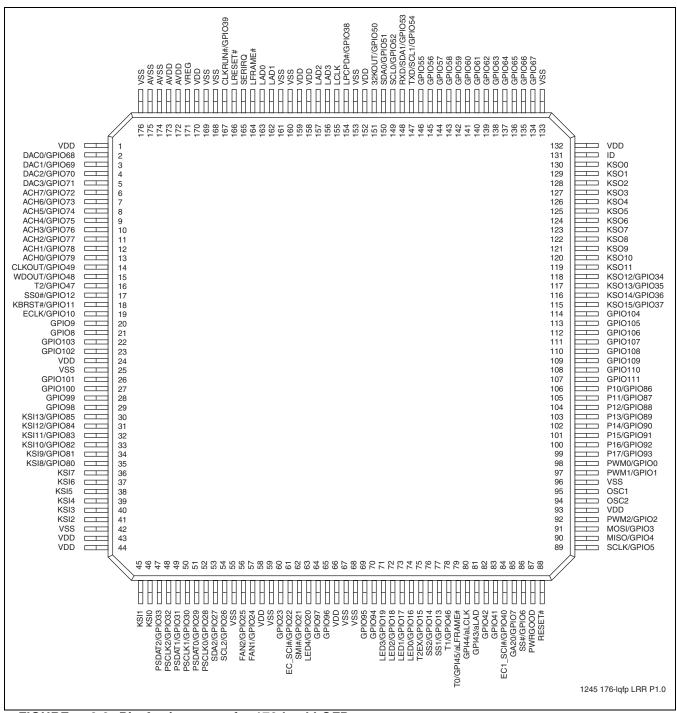

| FIGURE 2-2: Pin Assignments for 176-lead LQFP 17                                  |

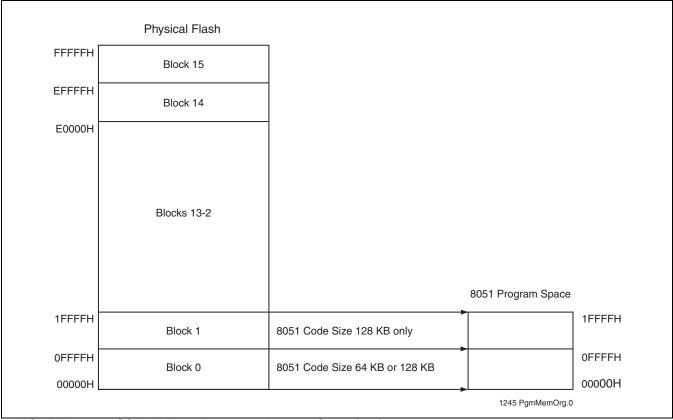

| FIGURE 3-1: SST79LF008 Program Memory Organization                                |

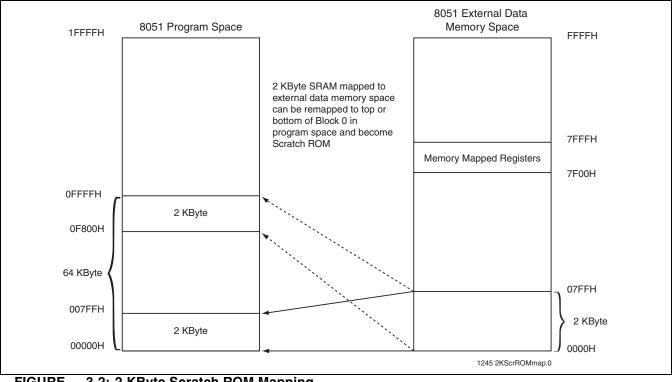

| FIGURE 3-2: 2 KByte Scratch ROM Mapping                                           |

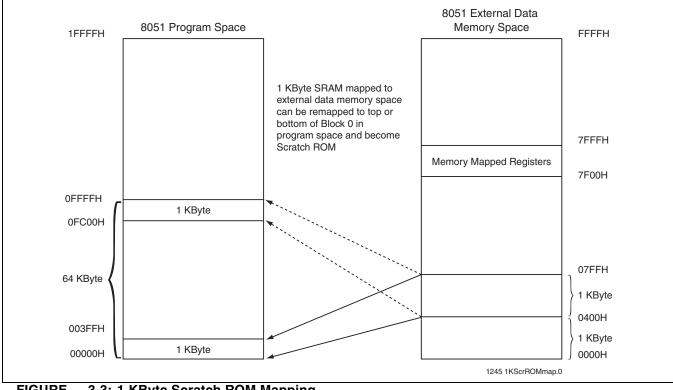

| FIGURE 3-3: 1 KByte Scratch ROM Mapping 26                                        |

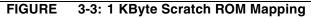

| FIGURE 3-4: 512 Byte Scratch ROM Mapping 27                                       |

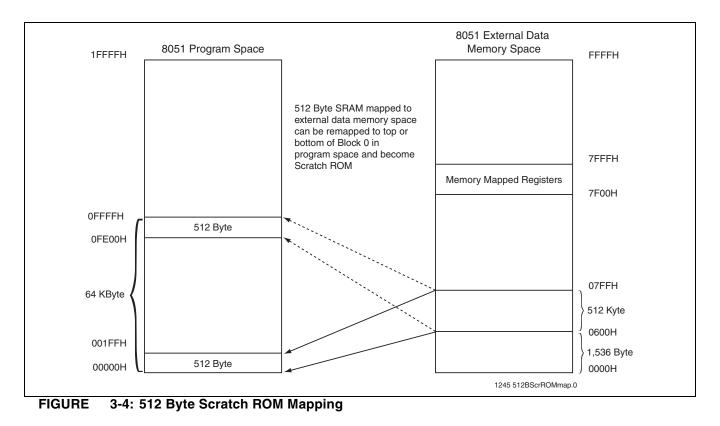

| FIGURE 3-5: 256 Byte Scratch ROM Mapping 27                                       |

| FIGURE 3-6: SST79LF008 Data Memory Organization                                   |

| FIGURE 4-1: SST79LF008 Flash Memory Map 44                                        |

| FIGURE 4-2: Shared ROM Interface                                                  |

| FIGURE 4-3: IAP Sector-Erase                                                      |

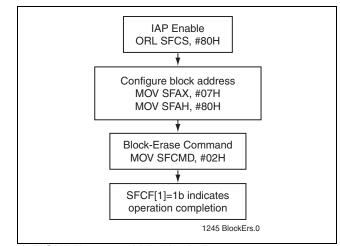

| FIGURE 4-4: IAP Block-Erase                                                       |

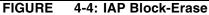

| FIGURE 4-5: IAP Word-Program                                                      |

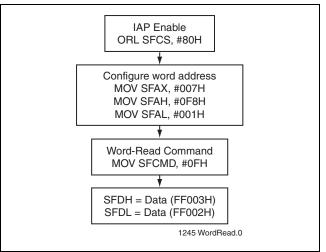

| FIGURE 4-6: IAP Word-Read                                                         |

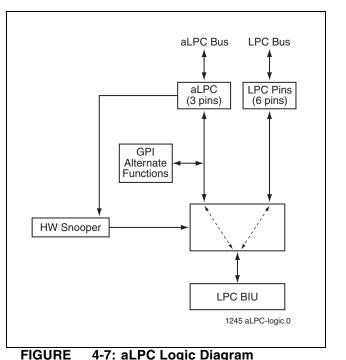

| FIGURE 4-7: aLPC Logic Diagram                                                    |

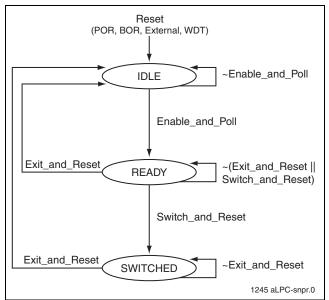

| FIGURE 4-8: aLPC Snooper State Machine                                            |

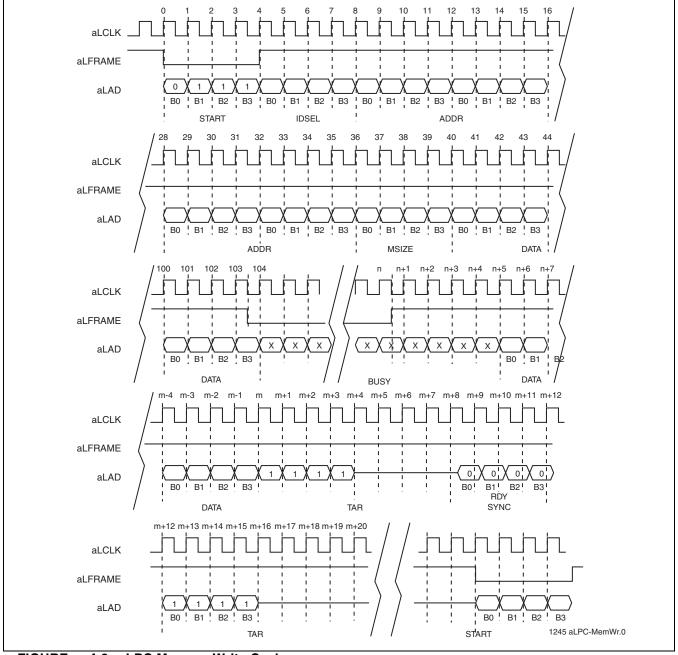

| FIGURE 4-9: aLPC Memory Write Cycle 59                                            |

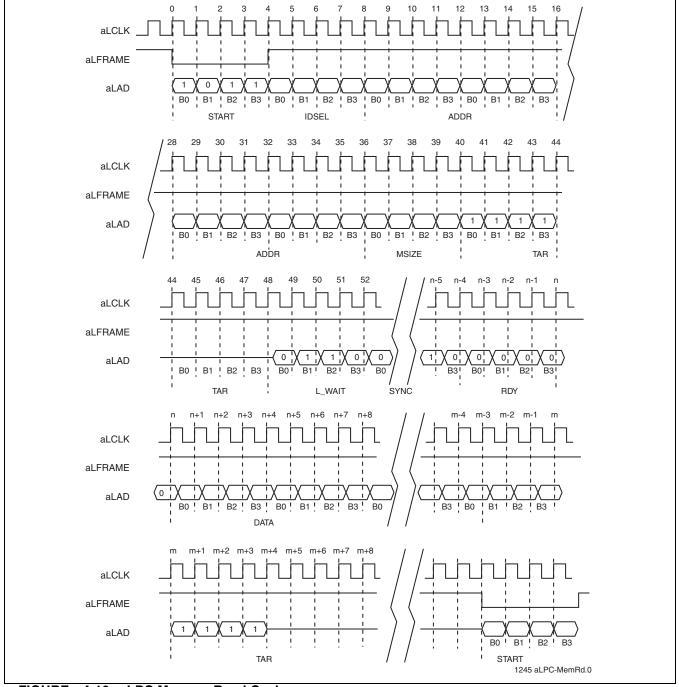

| FIGURE 4-10: aLPC Memory Read Cycle 61                                            |

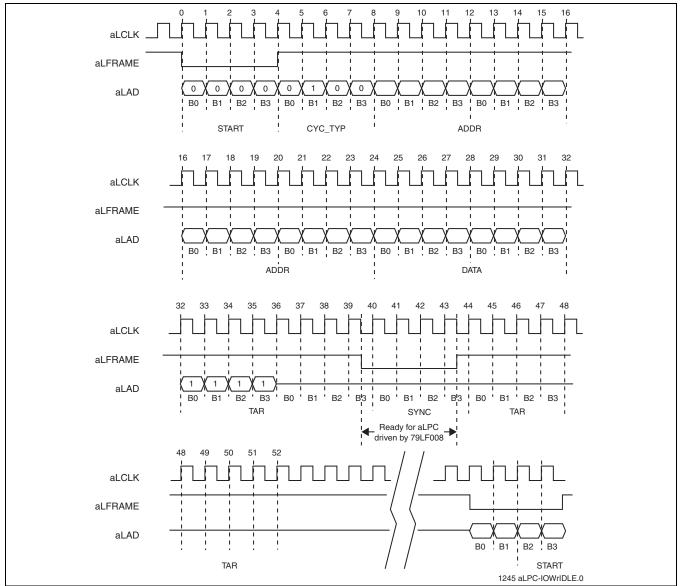

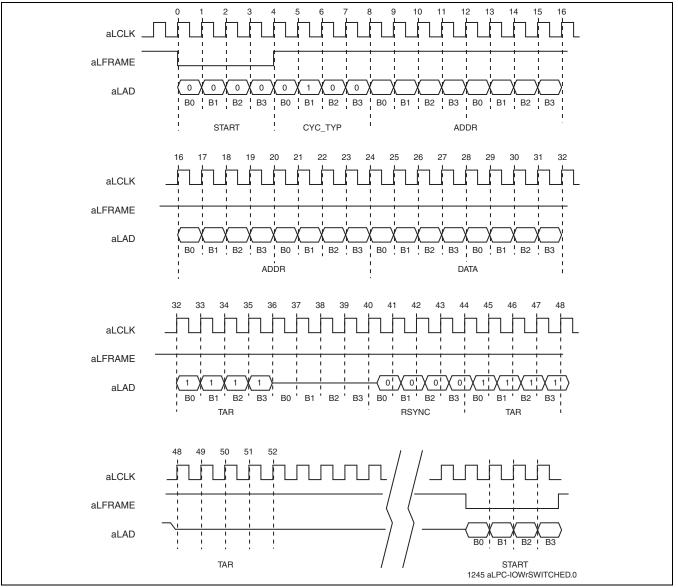

| FIGURE 4-11: aLPC I/O Write Cycle (IDLE or READY state)                           |

| FIGURE 4-12: aLPC I/O Write cycle (SWITCHED state)                                |

| FIGURE 5-1: Reset Block Diagram                                                   |

| FIGURE 5-2: External Reset Circuit                                                |

| FIGURE 5-3: Crystal Oscillator Circuit                                            |

| FIGURE 5-4: SST79LF008 Clock Selection                                            |

| FIGURE 5-5: Power-On Sequence and Core Clock Switching                            |

| FIGURE 5-6: Clock Switching after Waking up from Power Down Mode                  |

| FIGURE 6-1: Dual Data Pointer Organization                                        |

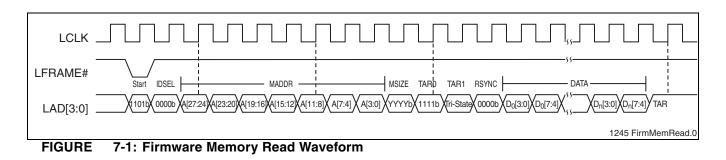

| FIGURE 7-1: Firmware Memory Read Waveform                                         |

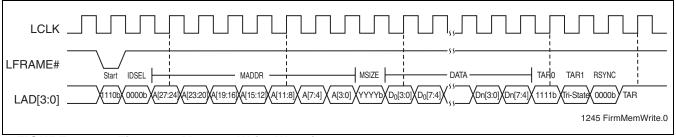

| FIGURE 7-2: Firmware Memory Write Waveform                                        |

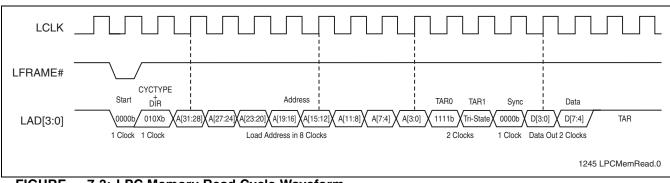

| FIGURE 7-3: LPC Memory Read Cycle Waveform                                        |

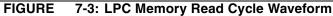

| FIGURE 7-4: LPC Memory Write Cycle Waveform                                       |

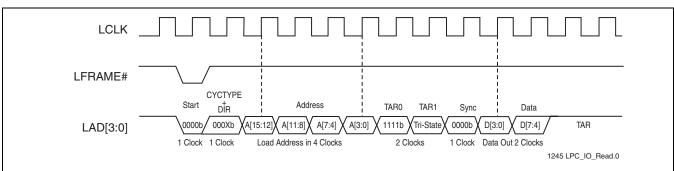

| FIGURE 7-5: LPC I/O Read Cycle Waveform                                           |

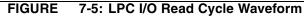

| FIGURE 7-6: LPC I/O Write Cycle Waveform                                          |

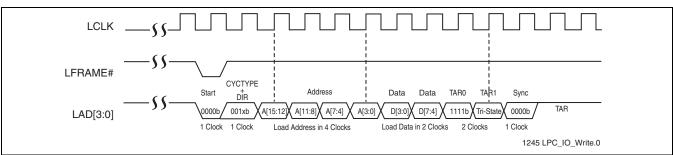

| FIGURE 8-1: SST79LF008 Interrupt Structure (int1-int2)                            |

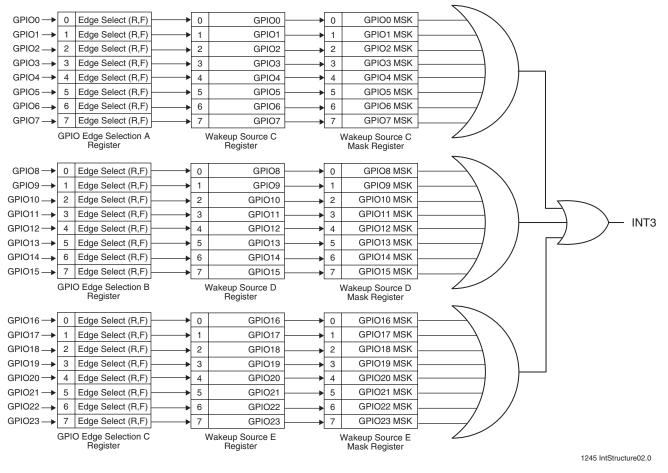

| FIGURE 8-2: SST79LF008 Interrupt Structure (int3) 100                             |

| FIGURE 8-3: SST79LF008 Interrupt Structure (int4) 101                             |

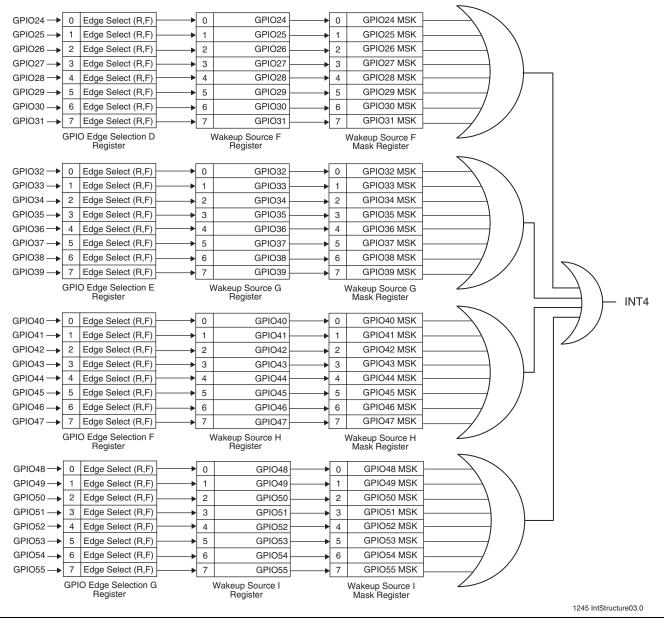

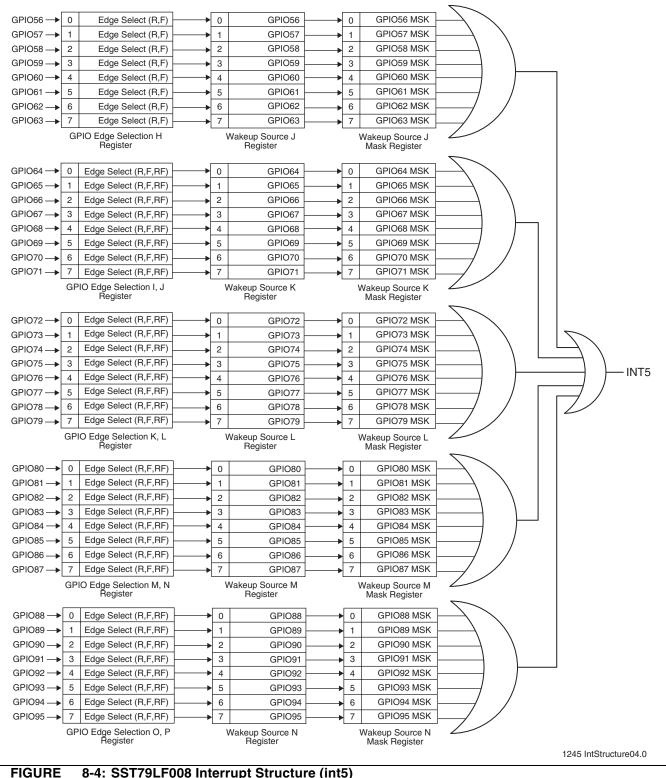

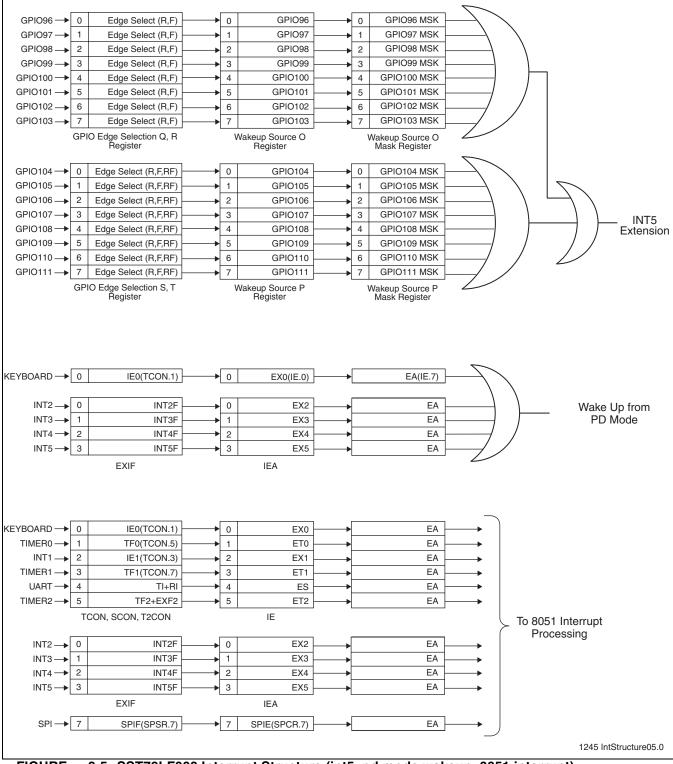

| FIGURE 8-4: SST79LF008 Interrupt Structure (int5) 102                             |

| FIGURE 8-5: SST79LF008 Interrupt Structure (int5, pd mode wakeup, 8051 interrupt) |

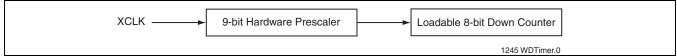

| FIGURE 10-1: Watchdog Timer                                                       |

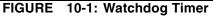

| FIGURE 10-2: Hibernation Timer                                                    |

| FIGURE 11-1: Framing Error Block Diagram                          |

|-------------------------------------------------------------------|

| FIGURE 11-2: UART Timings in Mode 1                               |

| FIGURE 11-3: UART Timings in Modes 2 and 3                        |

| FIGURE 12-1: SPI Master-Slave Interconnection 159                 |

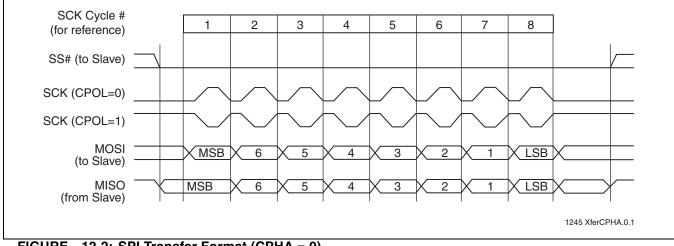

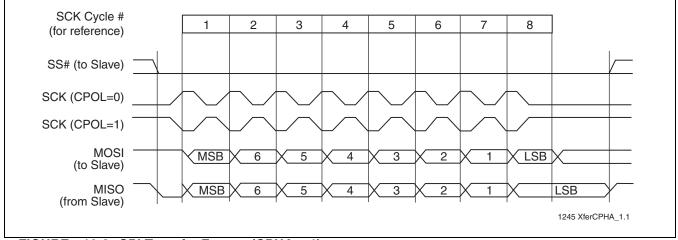

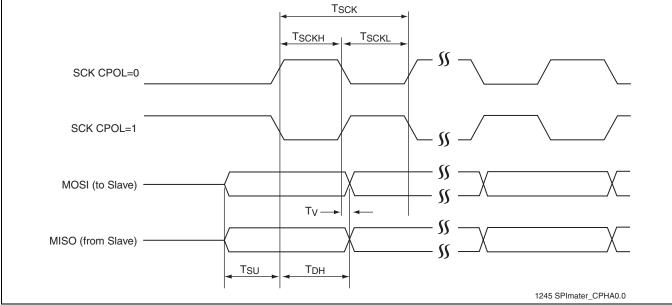

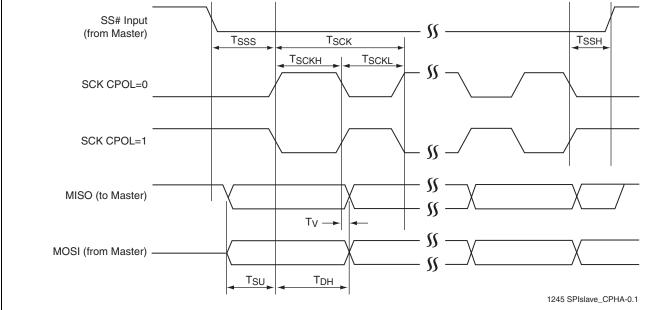

| FIGURE 12-2: SPI Transfer Format (CPHA = 0) 160                   |

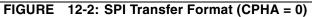

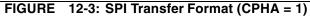

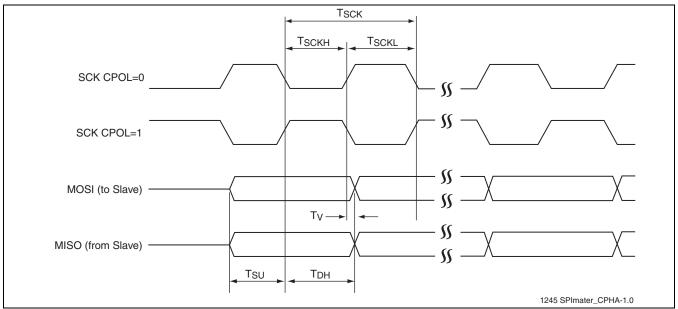

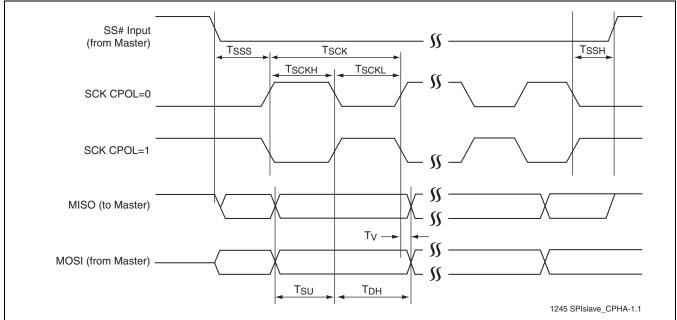

| FIGURE 12-3: SPI Transfer Format (CPHA = 1) 160                   |

| FIGURE 13-1: SMBus Module Block Diagram                           |

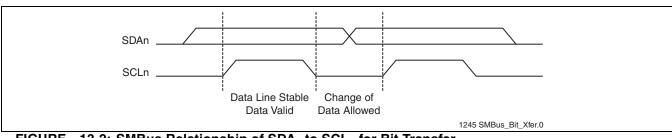

| FIGURE 13-2: SMBus Relationship of SDAn to SCLn for Bit Transfer  |

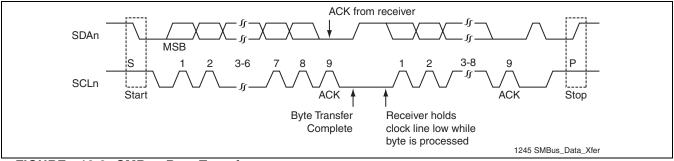

| FIGURE 13-3: SMBus Byte Transfer                                  |

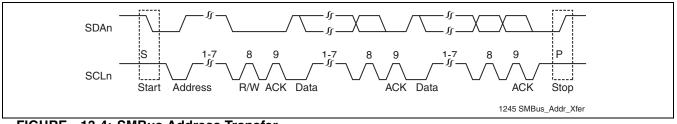

| FIGURE 13-4: SMBus Address Transfer                               |

| FIGURE 13-5: SMBus Master Transmit Mode Operation 172             |

| FIGURE 13-6: SMBus Master Receive Mode Operation 173              |

| FIGURE 13-7: SMBus Slave Transmit Mode Operation                  |

| FIGURE 13-8: SMBus Slave Receive Mode Operation 177               |

| FIGURE 13-9: SMBus Transmit/Receive Mode Switch                   |

| FIGURE 14-1: PS/2 Module Block Diagram 181                        |

| FIGURE 14-2: PS/2 Receive Protocol                                |

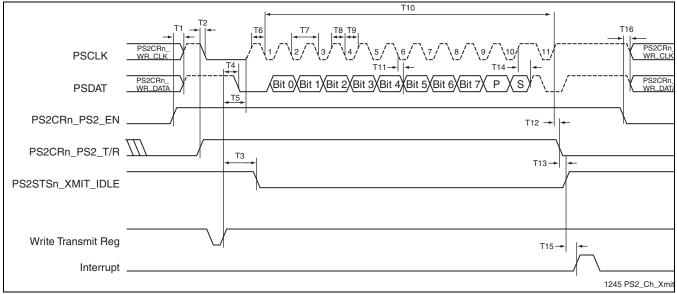

| FIGURE 14-3: PS/2 Transmit Protocol                               |

| FIGURE 15-1: Fan Tachometer Block Diagram 191                     |

| FIGURE 16-1: ADC Block Diagram 194                                |

| FIGURE 16-2: Example of ADC Operation (Single Mode) 198           |

| FIGURE 16-3: Example of ADC Operation (Continuous Mode) 200       |

| FIGURE 17-1: DAC Block Diagram                                    |

| FIGURE 18-1: KBC Interrupt Control 208                            |

| FIGURE 19-1: GA20 State Machine                                   |

| FIGURE 19-2: : Host and 8051 Control of GA20 212                  |

| FIGURE 20-1: SCI and SMI Generation Diagram 219                   |

| FIGURE 22-1: Serialized IRQ cycle                                 |

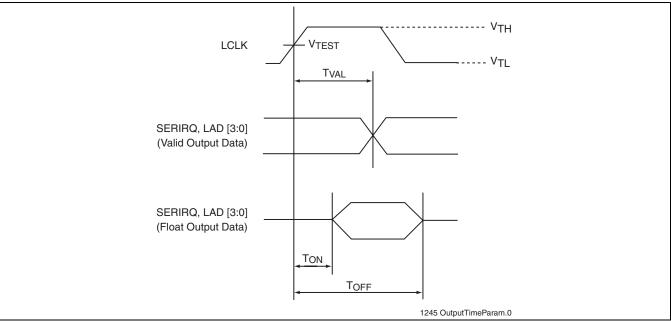

| FIGURE 24-1: AC Input/Output Reference Waveforms                  |

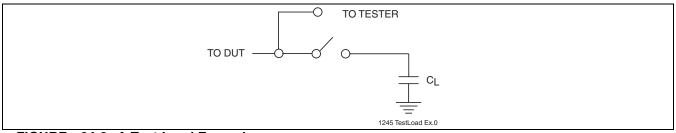

| FIGURE 24-2: A Test Load Example                                  |

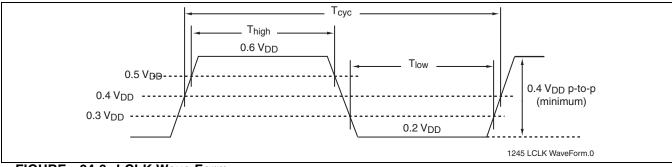

| FIGURE 24-3: LCLK Wave Form                                       |

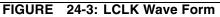

| FIGURE 24-4: LPC Output Timing Parameters                         |

| FIGURE 24-5: LPC Input Timing Parameters 236                      |

| FIGURE 24-6: LPC Reset Timing Diagram 237                         |

| FIGURE 24-7: External Input Clock Timing Diagram 238              |

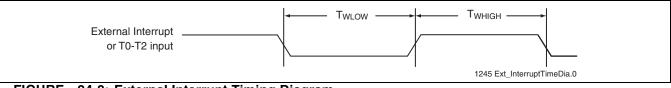

| FIGURE 24-8: External Interrupt Timing Diagram 238                |

| FIGURE 24-9: Power Up and External Reset Timing Diagram           |

| FIGURE 24-10: SMBus Timing Diagram                                |

| FIGURE 24-11: PS/2 Hardware State Machine Receive Timing Diagram  |

| FIGURE 24-12: PS/2 Hardware State Machine Transmit Timing Diagram |

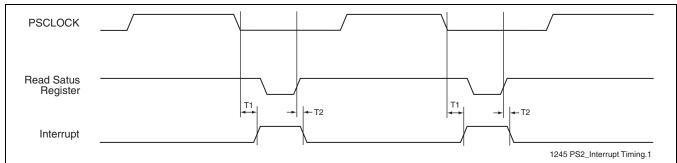

| FIGURE 24-13: PS/2 Interrupt Timing in bit-banging mode 243       |

| FIGURE 24-14: UART Timing Diagram (Shift Register Mode)           |

| FIGURE 24-15: SPI Master Timing Diagram (CPHA=0, MSTR = 1) 245    |

| FIGURE 24-16: SPI Master Timing Diagram (CPHA=1, MSTR = 1)            | 245 |

|-----------------------------------------------------------------------|-----|

| FIGURE 24-17: SPI Slave Timing Diagram (CPHA=0, MSTR = 0)             | 246 |

| FIGURE 24-18: SPI Slave Timing Diagram (CPHA=1, MSTR = 0)             | 246 |

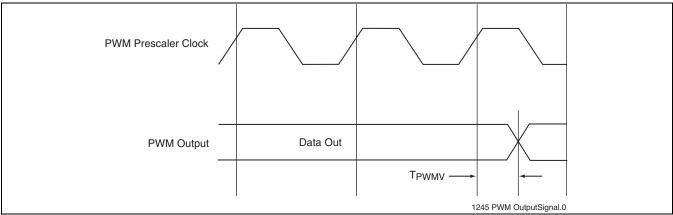

| FIGURE 24-19: PWM Output Signals Timing Diagram                       | 247 |

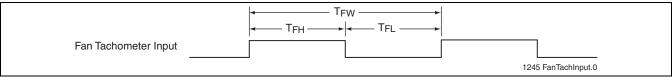

| FIGURE 24-20: FAN Tachometer Input Timing Diagram                     | 248 |

| FIGURE 24-21: aLPC Timing Diagram                                     | 248 |

| FIGURE 26-1: 176-lead Low-profile Quad Flat Pack                      | 251 |

| FIGURE 26-2: 176-ball Thin-profile Fine-pitch Ball Grid Array (TFBGA) | 252 |

# LIST OF TABLES

| TABLE | 2-1: Pin Descriptions                             | 18 |

|-------|---------------------------------------------------|----|

| TABLE | 2-2: I/O Buffer Types                             | 24 |

| TABLE | 3-1: Special Function Register Memory Map         | 29 |

| TABLE | 3-2: Miscellaneous SFRs Reference                 | 30 |

| TABLE | 3-3: Timer SFRs Reference                         | 30 |

| TABLE | 3-4: UART SFRs References                         | 31 |

| TABLE | 3-5: SPI SFRs References                          | 31 |

|       | 3-6: GPIO Input MMCRs References                  |    |

|       | 3-7: GPIO Output MMCRs References                 |    |

| TABLE | 3-8: GPIO Direction MMCRs References              | 33 |

|       | 3-9: GPIO Function Selection MMCRs References     |    |

|       | 3-11: Interrupt Source MMCRs References           |    |

| TABLE | 3-10: GPIO Active Edge Selection MMCRs References | 35 |

| TABLE | 3-12: Wakeup Source MMCRs References              | 36 |

| TABLE | 3-13: Timer MMCRs References                      | 37 |

|       | 3-14: PWM MMCRs References                        |    |

|       | 3-15: SMBus MMCRs References                      |    |

| TABLE | 3-16: PS/2 MMCRs References.                      | 38 |

| TABLE | 3-17: Fan Tachometer MMCRs References             | 38 |

|       | 3-18: ADC MMCRs References                        |    |

|       | 3-19: DAC MMCRs References                        |    |

|       | 3-20: KBC Host Interface MMCRs References         |    |

| TABLE | 3-21: GA20 Control MMCRs References.              | 39 |

|       | 3-22: ACPI EC Interface MMCRs References          |    |

|       | 3-23: MailBox MMCRs References                    |    |

|       | 3-24: Configuration MMCRs References              |    |

|       | 3-25: Miscellaneous MMCRs References              |    |

|       | 4-1: ENVR Address Space                           |    |

|       | 4-2: UNVR Address Space                           |    |

|       | 4-3: Scratch ROM Mapping                          |    |

|       | 4-4: IAP Commands for SST79LF008                  |    |

|       | 4-5: OVERLAY Bit Value After RESET                |    |

| TABLE | 4-6: aLPC Snooper Command Sequences               | 55 |

|       | 4-7: aLPC Pin Descriptions                        |    |

|       | 4-8: aLPC Memory Write Cycle Field Definitions    |    |

| TABLE | 4-9: aLPC Memory Read Cycle Field Definitions.    | 60 |

|       | 4-10: aLPC I/O Write Cycle Field Definitions      |    |

|       | 4-11: aLPC Bus Flash Command Definitions          |    |

|       | 5-1: SST79LF008 Reset Sources                     |    |

|       | 5-2: SST79LF008 Clock Sources                     |    |

| TABLE | 5-3: Crystal Oscillator Circuit Components        | 71 |

|       |                                                   |    |

|                                                                               | 5-4: Clock Domains for SST79LF008 Modules                                                                                                                                                                                                                                                                                                                                                       | 72                                                                                                                                                                                          |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TABLE                                                                         | 6-1: 17-bit Addressing Mode-Specific Instructions                                                                                                                                                                                                                                                                                                                                               | 78                                                                                                                                                                                          |

| TABLE                                                                         | 7-1: Transfer Size Supported by the SST79LF008                                                                                                                                                                                                                                                                                                                                                  | 82                                                                                                                                                                                          |

| TABLE                                                                         | 7-2: Firmware and LPC Memory Cycles START Field Definition                                                                                                                                                                                                                                                                                                                                      | 82                                                                                                                                                                                          |

| TABLE                                                                         | 7-3: Firmware Memory Read Cycle Field Definitions.                                                                                                                                                                                                                                                                                                                                              | 83                                                                                                                                                                                          |

| TABLE                                                                         | 7-4: Firmware Memory Write Cycle Field Definitions.                                                                                                                                                                                                                                                                                                                                             | 84                                                                                                                                                                                          |

|                                                                               | 7-5: LPC Memory Read Cycle Field Definitions.                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                             |

| TABLE                                                                         | 7-6: LPC Memory Write Cycle Field Definitions.                                                                                                                                                                                                                                                                                                                                                  | 86                                                                                                                                                                                          |

|                                                                               | 7-7: LPC I/O Read Cycle Field Definitions.                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                             |

| TABLE                                                                         | 7-8: LPC I/O Write Cycle Field Definitions                                                                                                                                                                                                                                                                                                                                                      | 88                                                                                                                                                                                          |

|                                                                               | 7-9: LPC Flash Command Definitions1                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                             |

| TABLE                                                                         | 7-10: Product Identification                                                                                                                                                                                                                                                                                                                                                                    | 90                                                                                                                                                                                          |

| TABLE                                                                         | 7-11: Valid MSIZE Field for Firmware Memory Cycle                                                                                                                                                                                                                                                                                                                                               | 92                                                                                                                                                                                          |

| TABLE                                                                         | 7-12: Block Locking Registers                                                                                                                                                                                                                                                                                                                                                                   | 94                                                                                                                                                                                          |

|                                                                               | 7-13: Block Locking Register Bits                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                             |

|                                                                               | 7-14: JEDEC ID Registers                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                             |

|                                                                               | 7-15: Multi-byte Read/Write Configuration registers                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                             |

|                                                                               | 7-16: Unique ID Registers                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                             |

|                                                                               | 8-1: SST79LF008 Interrupt Sources                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                             |